Add to Cart

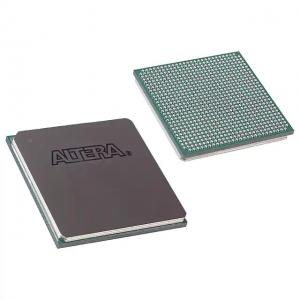

EP4SGX110DF29C4Nの産業電子部品FBGA-780

| 製品特質 | 属性値 |

|---|---|

| Intel | |

| FPGA -システム内プログラム可能なゲート・アレー | |

| Stratix IV GX | |

| 372入力/出力 | |

| 900 mV | |

| 0 C | |

| + 70 C | |

| SMD/SMT | |

| FBGA-780 | |

| 皿 | |

| データ転送速度: | 600 Mb/sから8.5 Gb/s |

| シリーズ: | Stratix IV GX |

| ブランド: | Intel/Altera |

| 最高の動作周波数: | 600のMHz |

| 敏感な湿気: | はい |

| トランシーバーの数: | 8トランシーバー |

| 製品タイプ: | FPGA -システム内プログラム可能なゲート・アレー |

| 工場パックの量: | 36 |

| 下位範疇: | プログラム可能な論理IC |

| 商号: | Stratix |

特徴の概要

次のリストはStratix IV装置家族の特徴を要約する:

■Stratix IV GXの48までの双方向通信の司令官ベースのトランシーバーおよびデータ転送速度を支えるまでGT装置

8.5 Gbpsおよび11.3 Gbps、それぞれ

■プログラム可能な送信機の前重点およびfrequency-dependent損失を補う受信機の同等化の回路部品

物理的な媒体

■3.125 Gbpsの100 MWおよび6.375 Gbpsの135 MWの典型的で物理的な中型の付属品(PMA)のパワー消費量每の

チャネル

■72,600への装置ごとの813,050同等のLEs

■本当のデュアル ポートの記憶を実行する3つのRAMのブロック サイズから成っているTriMatrixの高められた記憶の7,370から33,294 Kb

そして先入れ先出し法の緩衝

■9つのx 9ビット、12のx 12ビット、18のx 18ビットおよび36のx 36ビット全精密として構成可能高速デジタル信号処理の(DSP)ブロック

600までのMHzの乗数

■16個までの全体的な時計(GCLK)、88個の地方時計(RCLK)、および装置ごとの132個の周囲の時計(PCLK)

■DDR、DDR2、DDR3 SDRAM、RLDRAM II、QDR II、およびQDR II+を含む高速外的な記憶インターフェイスのためのサポート

24までのモジュラー入力/出力銀行のSRAM

■serializer/並直列交換回路(SERDES)、動的段階の直線(DPA)、およびソフト司令官の回路部品が付いている高速LVDS入力/出力サポートの

データ転送速度1.6までGbps

■源同期バス標準のためのサポート、SGMIIを含んで、GbEのSPI-4段階2 (POS-PHYのレベル4)、SFI-4.1、XSBI、

ユートピアIV、NPSIおよびCSIX-L1

■Stratix IIIからの最低PCBの影響とのStratix IV Eに設計の移動を許可するように設計されているStratix IV E装置のためのPinouts。